Traditional outlier and quality control methodologies often assume that data will conform to ideal, Gaussian distributions. In practice, this is rarely the case. Upstream variability in manufacturing—ranging from process variation to equipment inconsistencies—can significantly impact the behavior of otherwise good die. Identifying subtle yield detractors requires examining a broader set of wafer-level test parameters and their data signatures. These signatures may follow non-Gaussian distributions such as Log-Normal, Uniform, Chi-Square, or Multi-Modal, and must be analyzed in conjunction with spatial considerations like wafer zonal effects.

How yieldWerx Overcomes These Gaps

yieldWerx’s Advanced Part Average Test (PAT) was purpose-built to address these real-world complexities. It evaluates data signatures for every test and die, across multiple dimensions—such as reticle site, probe site, and wafer zone. yieldWerx then dynamically applies PAT rules, whether defined by the user or intelligently selected based on the actual data distribution. The system supports user override, full automation, or hybrid configurations where the platform suggests optimized rule types.

Behind the scenes, yieldWerx continuously monitors key metrics for every device, recipe, lot, and wafer, including:

- How often user-defined rules are overridden

- How often suboptimal rules were executed due to user enforcement

- When yieldWerx self-learns and applies optimal rule logic

These KPIs are accessible in real-time dashboards, giving users complete transparency. AI/ML integration enables predictive yield modeling and real-time alerting for drift, anomalies, and variation.

Fixing Process Issues Proactively

When yield signatures begin to fluctuate across wafers or lots, it can indicate underlying process or hardware issues. yieldWerx Advanced PAT, in combination with its Advanced Lot Correlation & Commonality Engine, helps identify systemic root causes quickly. From tool variation and chamber drift to probe card degradation and reticle-specific behavior, yieldWerx uncovers correlations across multi-dimensional test data. Engineers can instantly compare good vs. failing lots to isolate root causes, enabling faster corrective action and potentially saving millions in yield loss.

Future-Proofing for Advanced Devices

As the semiconductor industry evolves toward chiplets, 3D stacking, and heterogeneous integration, yieldWerx’s PAT system adapts with it. The engine generalizes across device families, leverages historical learning during new ramps, and auto-adjusts for probe or binning behavior. Through deep integration with yieldWerx’s Lot Genealogy and Commonality Analysis, users can view PAT behavior in the context of the entire product lifecycle—from WAT/PCM to Assembly, Final Test, and Burn-In. With a single click, users can trace data lineage down to individual parts, wafers, or source lots, refining not just PAT rules but also SPC, SBL, SYL, and Smart Wafer Map Merge (SWM) logic.

Coupled with Intelligent Rule Engines

yieldWerx’s PAT becomes exponentially more powerful when integrated with its advanced rule engines:

Nearest Neighbor Residual (NNR) Outlier Control

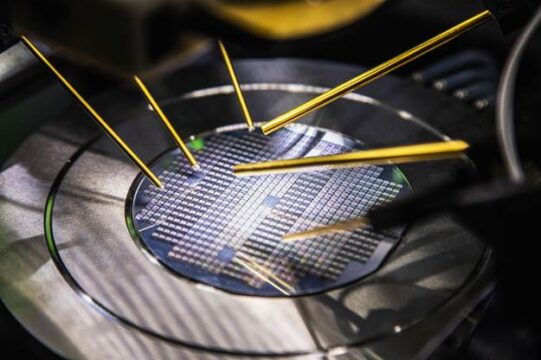

NNR compares each die’s measurements to its immediate spatial or logical neighbors—reticle, probe site, or wafer zone. By analyzing residuals between neighbors, yieldWerx flags localized anomalies often missed by global methods. This enhances binning accuracy, reduces systemic escape risk, and improves product reliability, especially in high-density designs.

Multi-Variant Part Average Testing

yieldWerx supports PAT rules based on multiple concurrent dimensions: device type, site, zone, condition, or temperature bin. Unlike single-rule PAT, Multi-Variant PAT segments the data into context-aware buckets with tailored control limits. Rules can span parameter families (e.g., multiple voltage tests) or disjoint parameters (e.g., timing and leakage), capturing cross-metric anomalies with precision.

Good Die in a Bad Neighborhood (GDBN) & GDBN-Z

GDBN identifies electrically passing die that reside in failing regions—flagging high-risk candidates for containment. GDBN-Z extends this to 3D ICs by analyzing vertical stacks across chiplets and dies, detecting spatial anomalies across layers. These insights help enforce zonal quarantines and avoid latent defect escapes.

Defect and Cluster Rules

yieldWerx bridges inline inspection with electrical test by enabling rule logic based on defect maps and spatial clustering. Rules can be triggered by defect density, proximity, or pattern recognition. Combined with test data, they allow holistic decisions rooted in both optical and electrical evidence. This supports better risk mitigation, traceability, and inline quality control.

Closing the Loop

Together, yieldWerx’s PAT, NNR, GDBN, Multi-Variant, and Defect/Cluster engines create a closed-loop quality management system. It not only detects outliers but explains their origin, supports process correction, and drives continuous yield improvement across the entire semiconductor product lifecycle.

yieldWerx stands alone as the only platform offering this comprehensive, end-to-end quality and outlier control solution—where real-time insight, intelligent automation, and full control remain in the hands of the engineer, with yieldWerx as a powerful co-pilot.