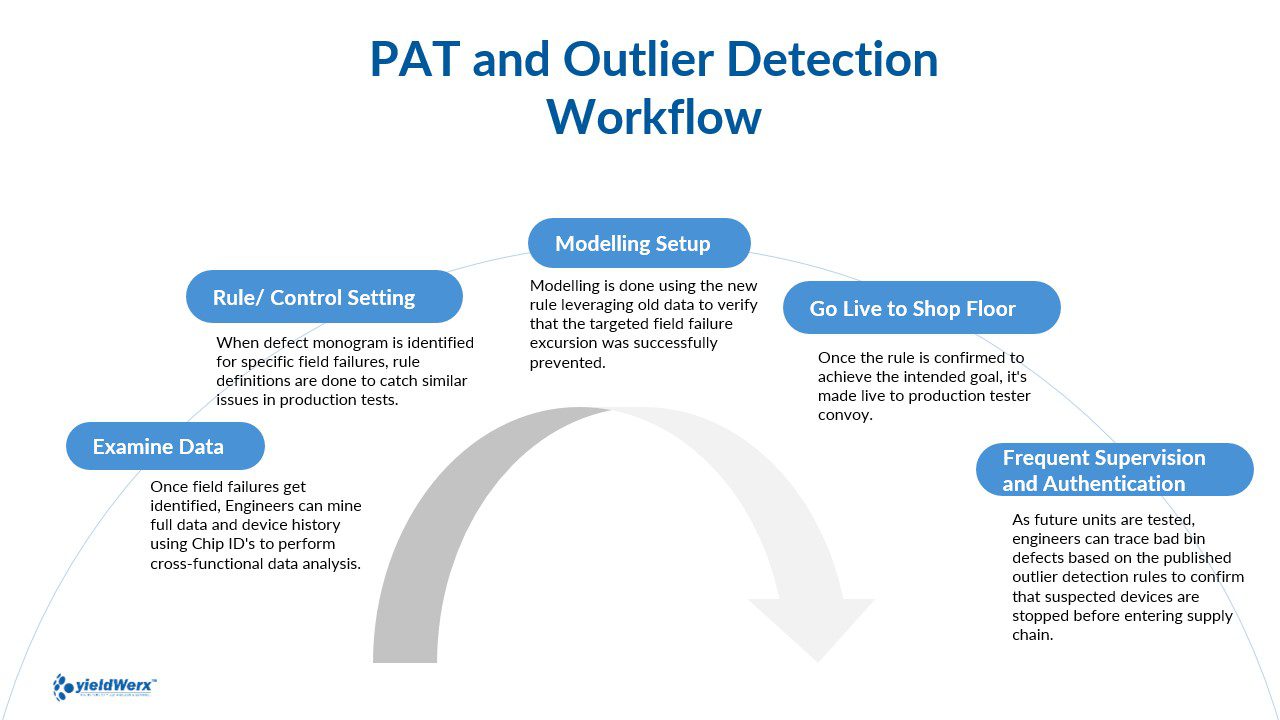

Latent defects not detected during manufacturing can have a catastrophic effect on product safety and reliability. The Quality Control module consists of 4 sub-modules that work together to prevent latent defects and detect outliers early.

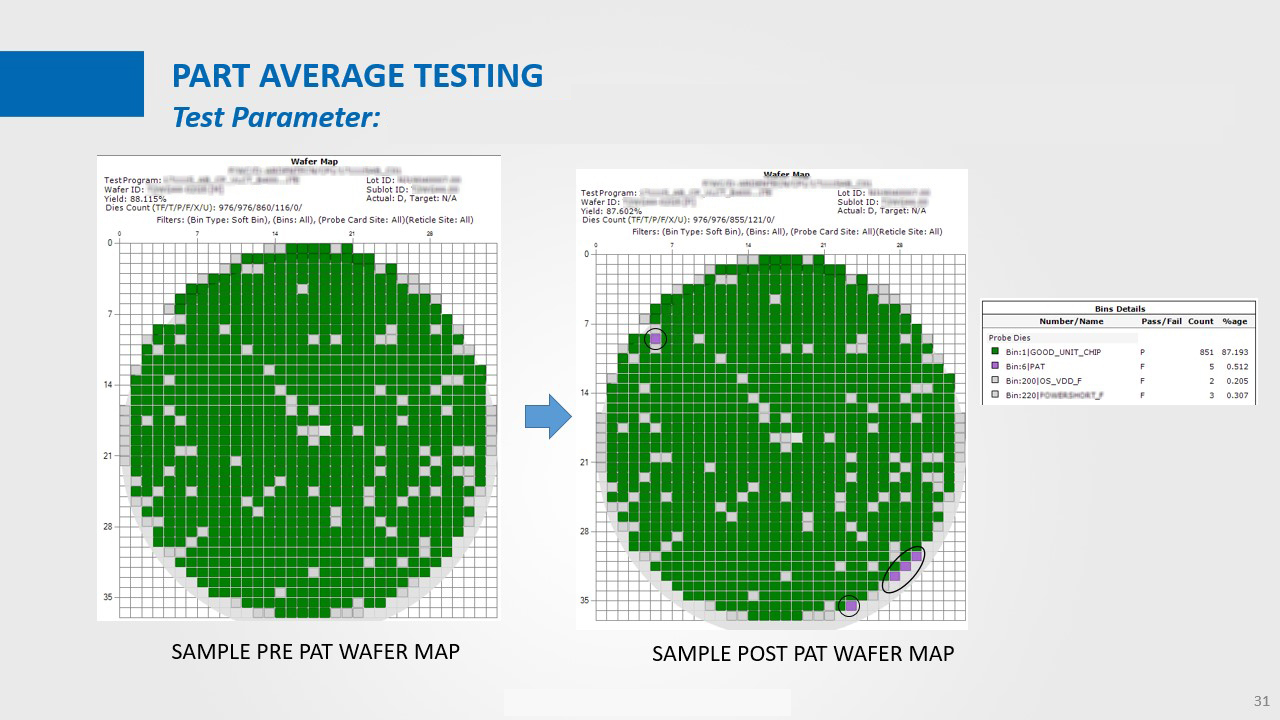

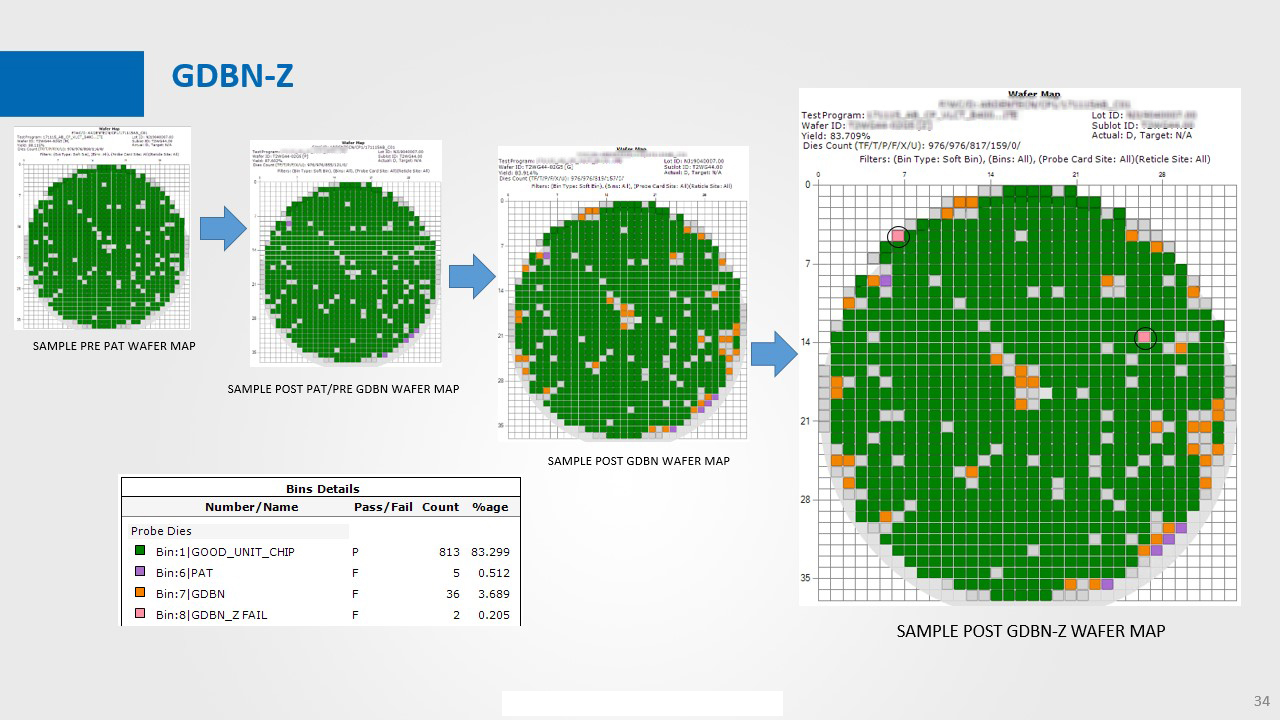

yieldWerx’s PAT methodology examines parametric

run-through and test outliers, geospacial defect patterns, reticle failures and historical anomalies (comparative to other wafers, lots and batches).

The test data from minimum six lots comprising of 5 zonally different die from wafer lots is analyzed using the static PAT limits of ###. If the distribution is not normal, then outliers are flagged and the limits are updated after a set interval of every eight wafer lots or a certain time period.

Dynamic PAT limits are calculated the same as Static PAT limits but use a “rolling” sample of “Passed” parts from the current lot to establish the mean and standard deviation (or appropriate non-gaussian limit). The results from “Passed” parts are re-analyzed after the lot (or wafer) is complete to determine if they fall outside of the Dynamic Pat Limits = ### using the tighter lot or wafer distribution. If they are “outliers” they are rejected despite passing the original USL, LSL limits.

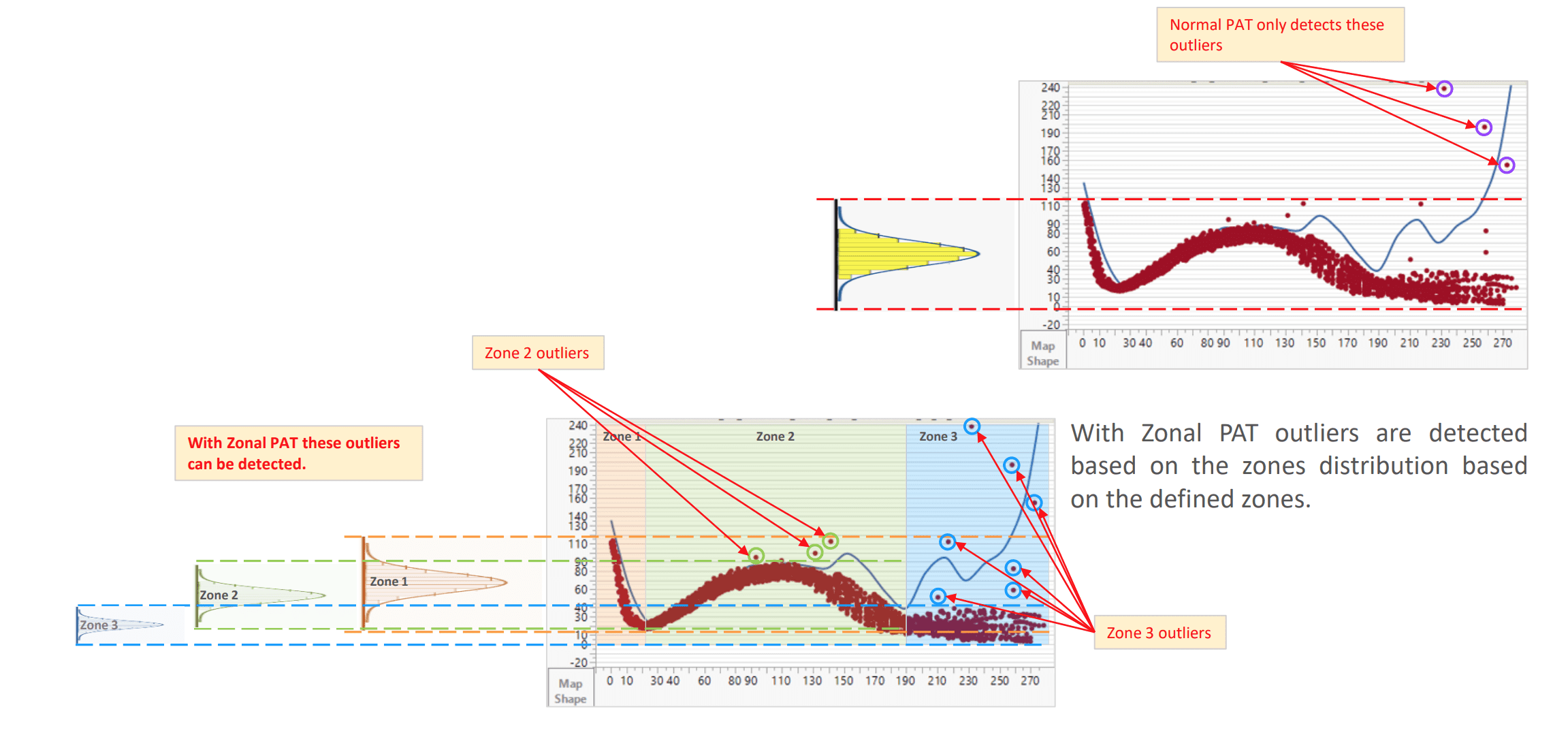

Zonal Part Average Test (ZPAT) is a statistical analysis technique used in semiconductor chip data analysis to evaluate the performance and yield of different zones on a chip or die. This method involves segmenting the chip into distinct zones and calculating the average yield or performance metrics for each zone. yieldWerx facilitates this analysis by allowing engineers to visualize and compare metrics across various zones, helping to identify localized issues or trends that may affect overall chip quality. Zones can be defined on the fly to allow engineers to conduct design of experiments and collaborate with process engineers. By focusing on these zonal averages, engineers can better understand the impact of specific manufacturing processes and optimize them accordingly, improving the reliability and yield of semiconductor products.

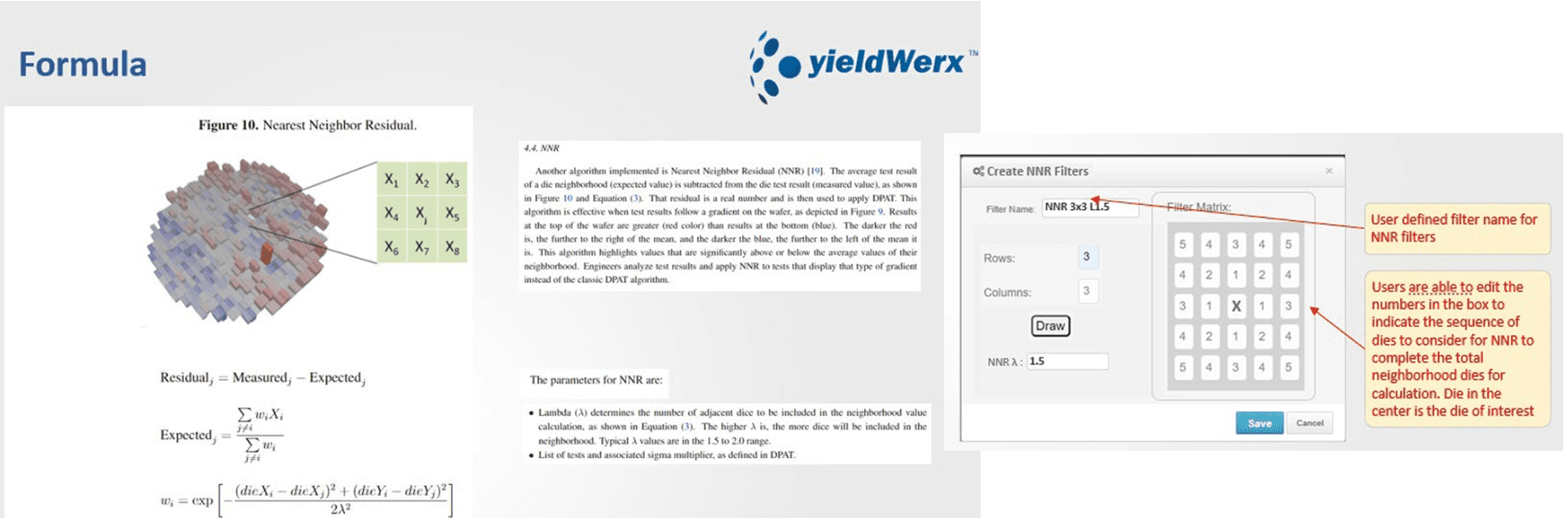

yieldWerx NNR helps in detecting anomalies by measuring how much a specific die deviates from similar dies in terms of yield, test results OR other quality metrics. This technique enhances the diagnostics process by pinpointing areas of concern more effectively, enabling engineers to focus on specific manufacturing processes or design elements that may require attention to improve overall yield and performance.

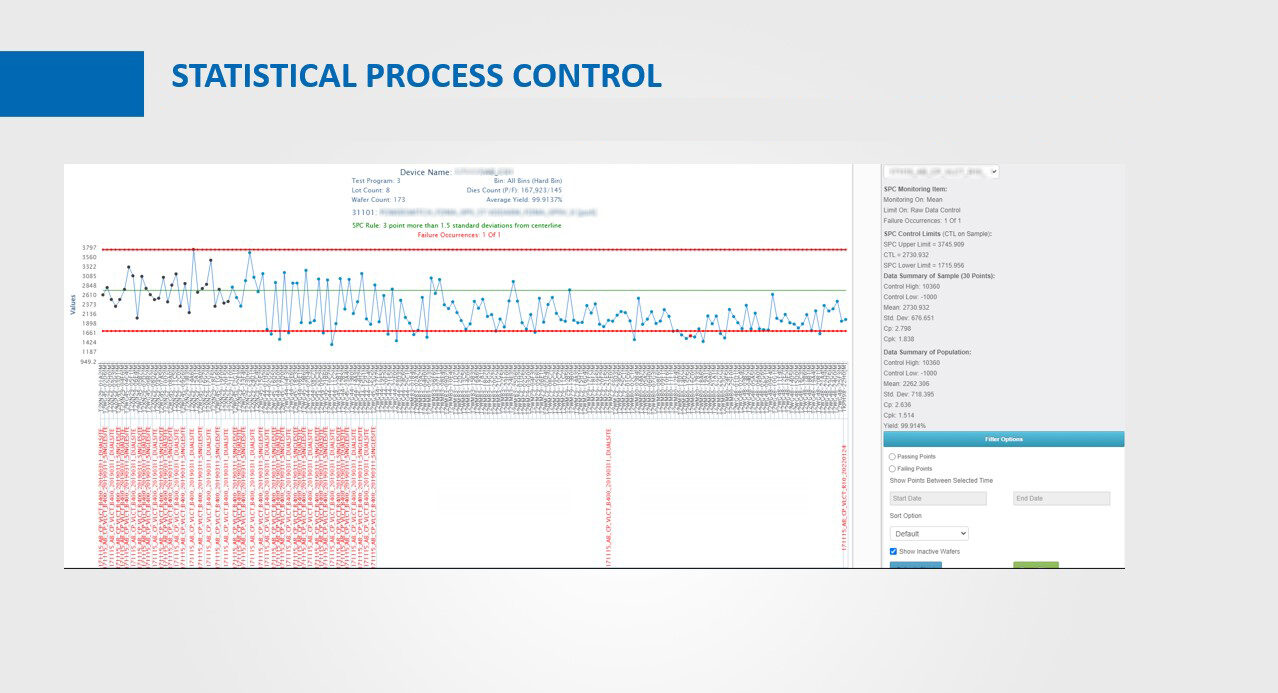

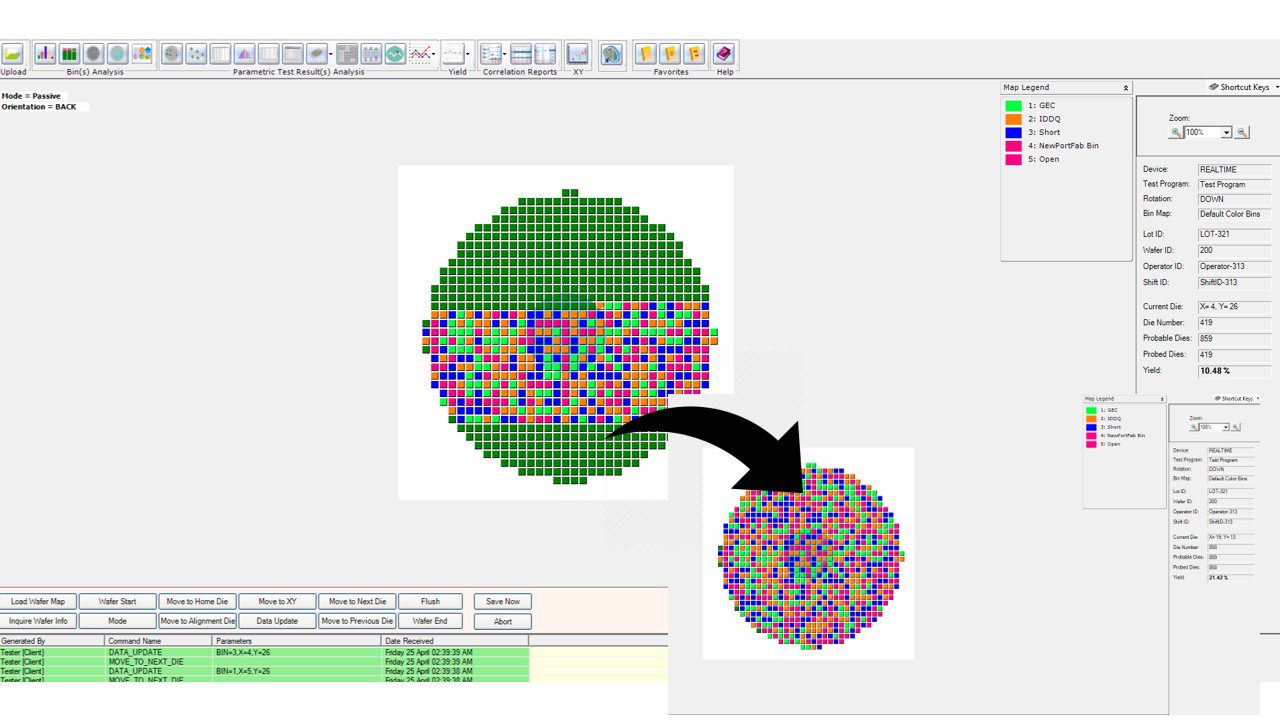

Statistical Process Control (SPC), Statistical Bin Limit (SBL), Statistical Yield (SYL) Monitoring functionality with the ability to define simple to complex rules. This module also handles work in progress as well as integration with MES and is equipped with a real-time alerting mechanism as well as mail digests notifications.

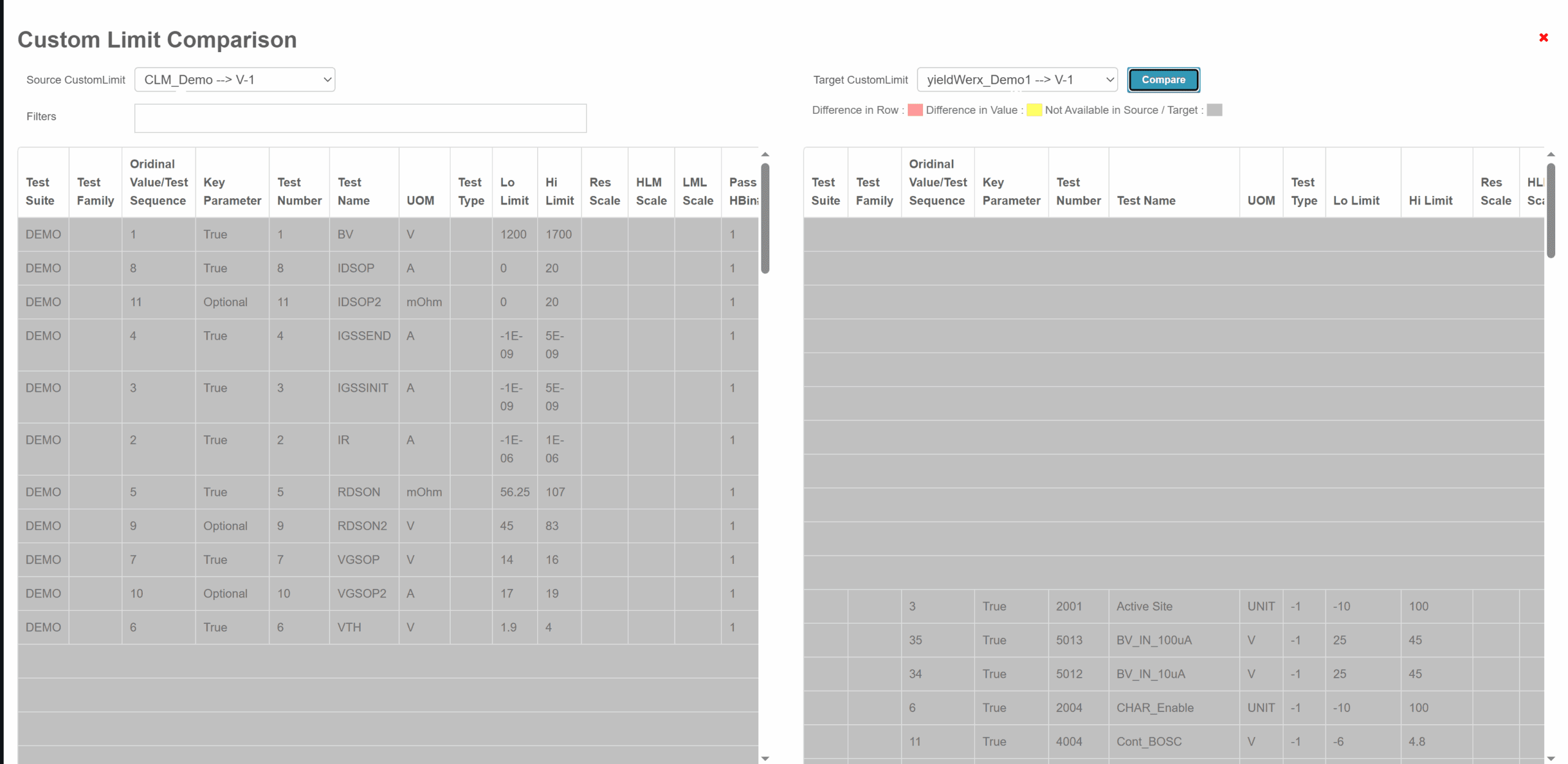

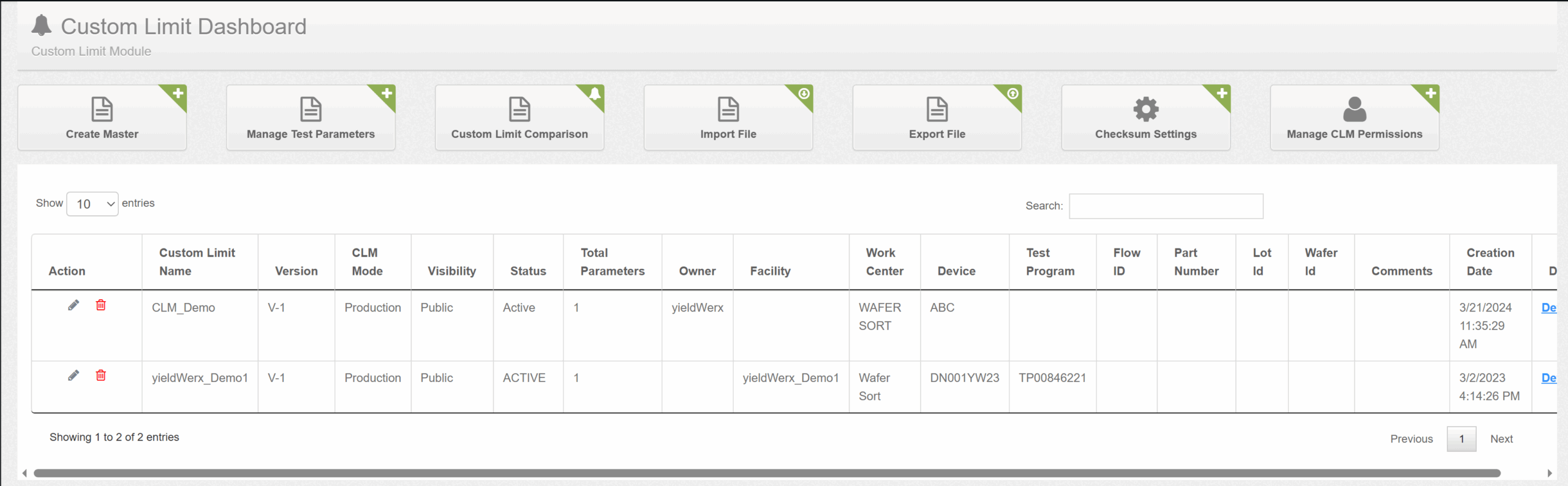

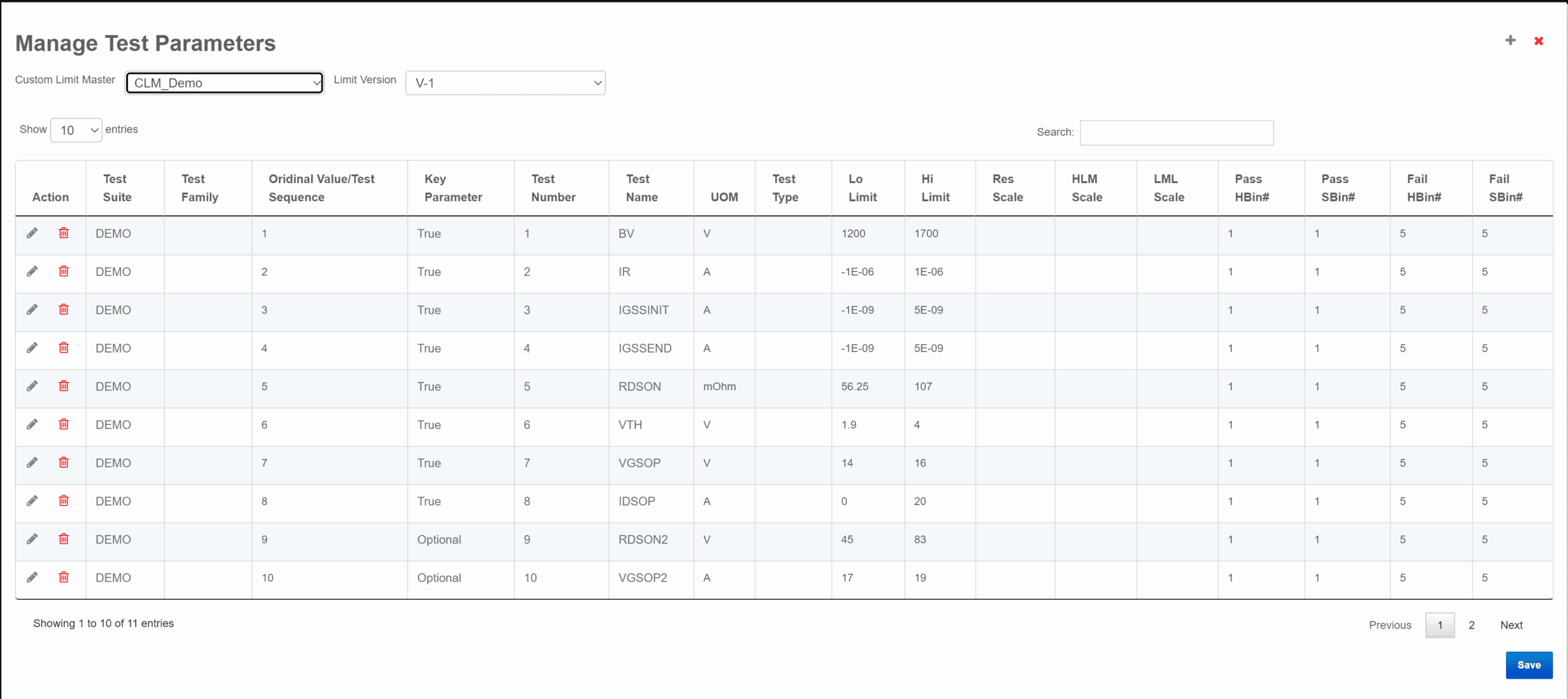

Conduct thorough what-if analysis with yieldWerx’s powerful custom limits manager. This tool enables control over customer-specific test program limits and corrective limits that can be adjusted, facilitating rebinning without the need for retesting. Additionally, the flexible binning feature allows for the postponement of binning until the final product stage, thereby enhancing operational flexibility and efficiency in testing and grading processes.