Synopsis:

Automatically collect inspection data and other images and associate this data to wafers/die/units and associated manufacturing equipment. For delivery of assembly maps use the data to apply business rules. For commonality analysis and root cause determination correlate image data with other data sources.

Description:

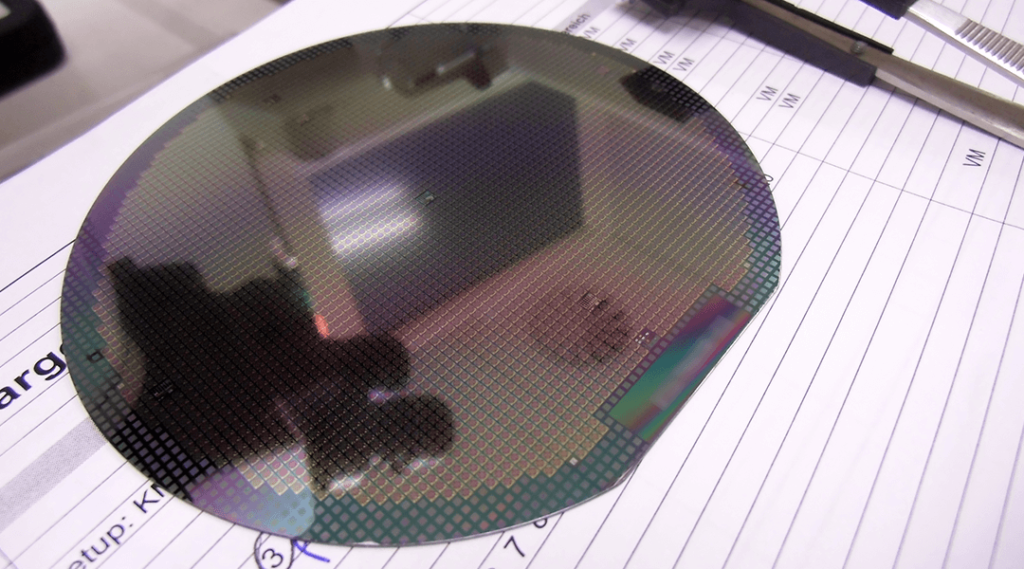

Throughout the semiconductor device manufacturing process inspection equipment scans devices and stores the resulting images. Scanning of wafers may be done on a sample basis yet the trend for advanced process nodes is to do 100% sampling at key process layers to manage the fabrication process. Images can detect particulates, scratches, and discoloration, such physical anomalies may not necessarily cause a faulty die- only an electronic test can determine this. Yet customer requirements or quality engineers may dictate that such physical anomalies necessitate failing the affected die/dies.

The image management module manages the business rules for creating assembly maps that use these business rules to flag die for failure even if they pass test results. Quality engineers can feed in business rules for lot and wafer holds for further disposition. Inspection image management module can, disposition- lot/wafers to be set on hold or request for additional testing.

Combining wafer image data with test data also enables product & quality engineers in their root-cause analysis of yield excursions. The image management module provides the equipment genealogy so that engineers are not wrangling data to figure this out.

Image management is agnostic to the types of images. This module can manage prevalent automated optical inspection tools such as KLA AUGUST 123 and Rudolph WHATEVER 456. Assembly cameras also take pictures during the manufacturing process as do some final test cells. Such data can be used in creative ways by engineers for process improvements, commonality analysis, and final test excursion management. Data from equipment can assist in quickly eliminating the equipment as the source of the issue and have engineers focus on the next possible pareto analysis.

Where applied:

- Wafer probe

- Assembly map generation

- Final test