Synopsis:

Ability to automatically construct image maps for memory or optical arrays using failing data and then running pattern recognition on it to determine failure types and to execute corresponding yield management decisions.

Description:

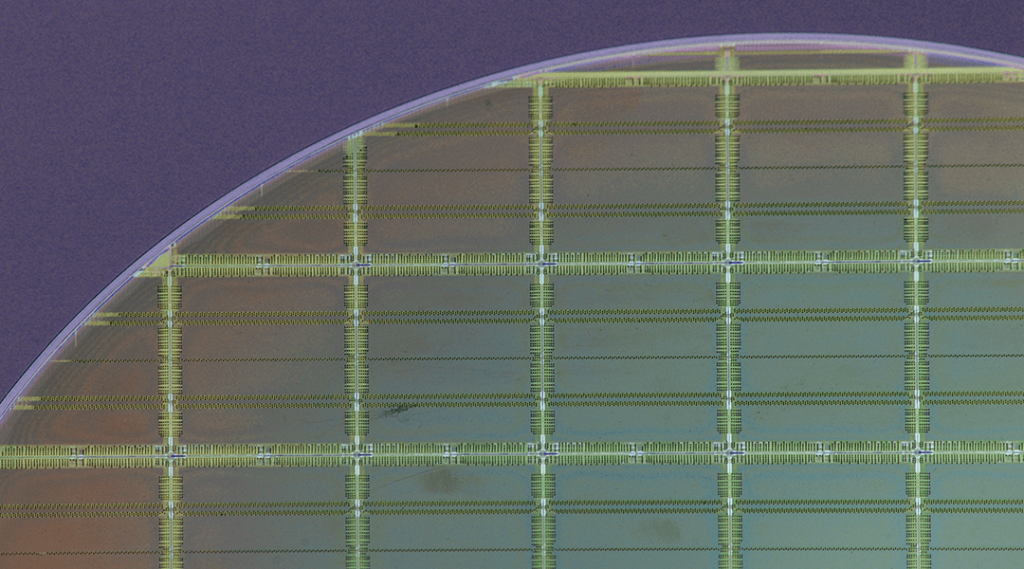

With this module, engineers can take advantage of the highly structured design of memory arrays and optical arrays. Does not matter whether these are stand-alone arrays or embedded in a system on a chip device or included as a chiplet in a 2.5D packaged device, array test data can be used by product, quality, and yield enhancement engineers. With a memory failure, the test program can provide a raster which gives you the P/F result on a bit cell basis for a particular test (e.g., March patterns for Static RAM).

This data can be used to create an image, or a fail bit-map of the array be it an array of optical elements or RAM. If the test program has an engineering data collection option, data from more than one array test can be used to create additional images. This module supports the subsequent pattern recognition to determine fail types such as a whole column or row failure or a cluster of cells failing at specific row and column coordinates. Overlay this data from multiple die or units the resulting patterns may indicate a yield excursion which requires a hold. The data can be used to inform physical failure analysis. With a higher sensitivity to fab defectivity rates, another action is to direct the test program to invoke a redundancy option.

Where applied:

- RMA

- Wafer test

- Final test